Copyright 2004, 2005 Hans Camenzind.

February 2005

This book is can be downloaded without fee from www.designinganalogchips.com

Re-publishing of any part or the whole is prohibited.

The author is indebted to the following for comments, suggestions and corrections:

Bob Pease, Jim Feit, Ted Bee, Jon Fischer, Tim Camenzind, Jules Jelinek, Brian Attwood, Ray Futrell, Beat Seeholzer, David Skurnik, Barry Schwartz, Dale Rebgetz, Tim Herklots, Jerry Gray, Paul Chic, Mark Leonard, Yut Chow, Gregory Weselak, Lars Jespersen and Wolfgang Horn.

### **Table of Contents**

| Analog World                |                                          |      |  |

|-----------------------------|------------------------------------------|------|--|

| 1 <b>Dev</b>                | ices                                     | 1-1  |  |

|                             | Semiconductors                           | 1-1  |  |

|                             | The Diode                                | 1-5  |  |

|                             | The Bipolar Transistor                   | 1-6  |  |

|                             | The Integrated Circuit                   | 1-13 |  |

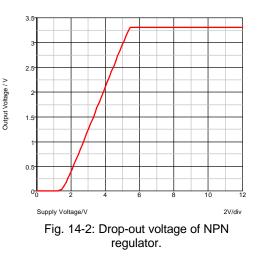

|                             | Integrated NPN Transistors               | 1-14 |  |

|                             | The Case of the Lateral PNP Transistor   | 1-22 |  |

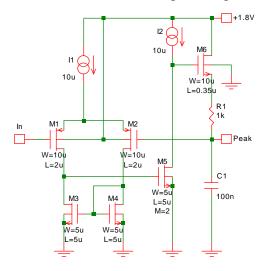

|                             | CMOS Transistors                         | 1-23 |  |

|                             | The Substrate PNP Transistor             | 1-27 |  |

|                             | Diodes                                   | 1-27 |  |

|                             | Zener Diodes                             | 1-28 |  |

|                             | Resistors                                | 1-29 |  |

|                             | Capacitors                               | 1-32 |  |

|                             | Other Processes                          | 1-33 |  |

|                             | CMOS vs. Bipolar                         | 1-34 |  |

| 2 Sim                       | ulation                                  | 2-1  |  |

|                             | What You Can Simulate                    | 2-2  |  |

|                             | DC Analysis                              | 2-2  |  |

|                             | AC Analysis                              | 2-3  |  |

|                             | Transient Analysis                       | 2-4  |  |

|                             | The Big Question of Variations           | 2-6  |  |

|                             | Models                                   | 2-8  |  |

|                             | The Diode Model                          | 2-8  |  |

|                             | The Bipolar Transistor Model             | 2-10 |  |

|                             | The Model for the Lateral PNP Transistor | 2-13 |  |

|                             | MOS Transistor Models                    | 2-14 |  |

|                             | Resistor Models                          | 2-16 |  |

|                             | Models for Capacitors                    | 2-17 |  |

|                             | Pads and Pins                            | 2-17 |  |

|                             | Just How Accurate is a Model?            | 2-18 |  |

|                             | rent Mirrors                             | 3-1  |  |

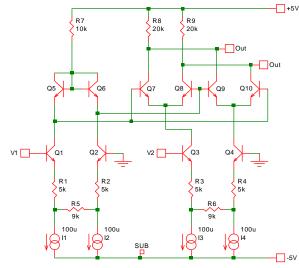

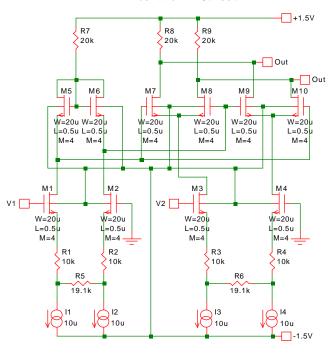

|                             | Royal Differential Pair                  | 4-1  |  |

| 5 Cur                       | rent Sources                             | 5-1  |  |

|                             | Bipolar                                  | 5-1  |  |

|                             | CMOS                                     | 5-7  |  |

|                             | The Ideal Current Source                 | 5-7  |  |

| 6 Time Out: Analog Measures |                                          | 6-1  |  |

|                             | dB                                       | 6-1  |  |

|                             | RMS                                      | 6-2  |  |

|                             | Noise                                    | 6-4  |  |

|                             | Fourier Analysis, Distortion             | 6-6  |  |

| 7 D                         | Frequency Compensation                   | 6-9  |  |

| 7 Ban                       | dgap References                          | 7-1  |  |

|                             | Low-Voltage Bandgap References           | 7-11 |  |

| CMOS Bandgap References                  | 7-13  |

|------------------------------------------|-------|

| 8 Op Amps                                | 8-1   |

| Bipolar Op-Amps                          | 8-1   |

| CMOS Op-Amps                             | 8-9   |

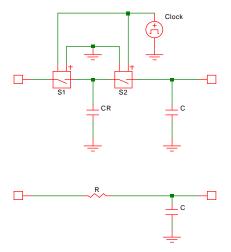

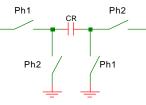

| Auto-Zero Op-Amps                        | 8-15  |

| 9 Comparators                            | 9-1   |

| 10 Transconductance Amplifiers           | 10-1  |

| 11 Timers and Oscillators                | 11-1  |

| Simulation of Oscillators                | 11-14 |

| LC Oscillators                           | 11-15 |

| Crystal Oscillators                      | 11-16 |

| 12 Phase-Locked Loops                    | 12-1  |

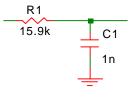

| 13 Filters                               | 13-1  |

| Active Filters, Low-Pass                 | 13-1  |

| High-Pass Filters                        | 13-6  |

| Band-Pass Filters                        | 13-6  |

| Switched-Capacitor Filters               | 13-8  |

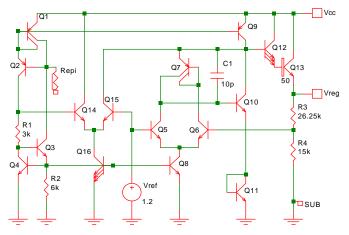

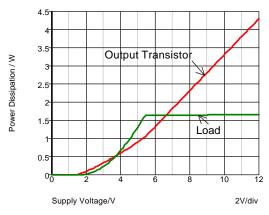

| 14 Power                                 | 14-1  |

| Linear Regulators                        | 14-1  |

| Low Drop-Out Regulators                  | 14-4  |

| Switching Regulators                     | 14-8  |

| Linear Power Amplifiers                  | 14-12 |

| Switching Power Amplifiers               | 14-15 |

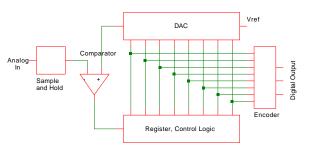

| 15 A to D and D to A                     | 15-1  |

| Digital to Analog Converters             | 15-1  |

| Analog to Digital Converters             | 15-7  |

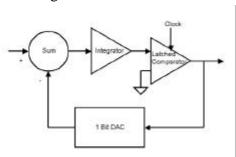

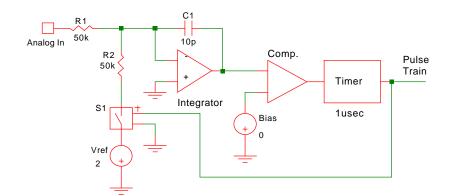

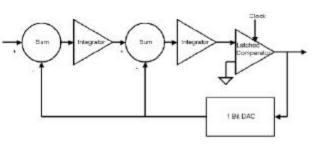

| The Delta-Sigma Converter                | 15-8  |

| 16 Odds and Ends                         | 16-1  |

| Gilbert Cell                             | 16-1  |

| Multipliers                              | 16-3  |

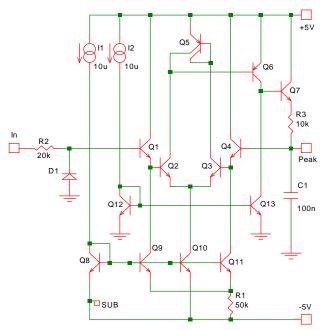

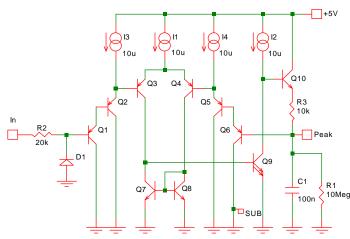

| Peak Detectors                           | 16-5  |

| <b>Rectifiers and Averaging Circuits</b> | 16-7  |

| Thermometers                             | 16-10 |

| Zero-Crossing Detectors                  | 16-12 |

| 17 Layout                                | 17-1  |

| Bipolar Transistors                      | 17-1  |

| Lateral PNP Transistors                  | 17-5  |

| Resistors                                | 17-6  |

| CMOS Transistors                         | 17-7  |

| Matching                                 | 17-9  |

| Cross-Unders                             | 17-10 |

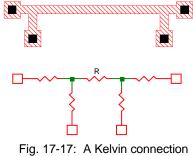

| Kelvin Connections                       | 17-11 |

| Metal Runs and Ground Connections        | 17-11 |

| Back-Lapping and Gold-Plating            | 17-12 |

| DRC and LVS                              | 17-12 |

| References                               |       |

| Index                                    |       |

# Analog World

"Everything is going digital". Cell phones, television, video disks, hearing aids, motor controls, audio amplifiers, toys, printers, what have you.

Analog design is obsolete, or will be shortly. Or so most people think.

Imminent death has been predicted for analog since the advent of the PC. But it is still here; in fact, analog ICs have been growing at almost exactly the same rate as digital ones. A digital video disk player has more analog content than the (analog) VCR ever did.

The explanation is rather simple: the world is fundamentally analog. Hearing is analog. Vision, taste, touch, smell, analog all. So is lifting and walking. Generators, motors, loud-speakers, microphones, solenoids, batteries, antennas, lamps, LEDs, laser diodes, sensors are fundamentally analog components.

The digital revolution is constructed on top of an analog reality. This fact simply won't go away. Somewhere, somehow you have to get into and out of the digital system and connect to the real world.

Unfortunately, the predominance and glamour of digital has done harm to analog. Too few analog designers are being educated, creating a void. This leaves decisions affecting analog performance to engineers with a primarily digital background.

In integrated circuits, the relentless pressure toward faster digital speed has resulted in ever-decreasing supply voltages, which are anathema to high-performance analog design. At 350nm (3.3V) there is still enough headroom for a high-performance analog design, though 5 Volts would be better. At 180nm (1.8V) the job becomes elaborate and time-consuming and performance starts to suffer. At 120nm (1.2V) analog design becomes very difficult even with reduced performance. At 90nm, analog design is all but impossible.

There are "mixed signal" processes which purportedly allow digital and analog circuitry on the same chip. A 180nm process, for example, will have some devices which can work with a higher supply voltage (e.g. 3 Volts). While such an addition is welcome (if marginal), the design data (i.e. models) are often inadequate and oriented toward digital design. Hence this book. It should give you an overview of the world of analog IC design, so that you can decide what kind of analog function can and cannot, should and should not be integrated. What should be on the same chip with digital and what should be separate. And, equally important, this book should enable you to ask the right questions of the foundry, so that your design works. The first time.

\* \* \*

You will find that almost all analog ICs contain a number of recognizable **circuit elements**, functional blocks with just a few transistors. These elements have proven useful and thus re-appear in design after design. Thus it makes sense to first look at such things as current mirrors, compound transistors, differential stages, cascodes, active loads, Darlington connections or current sources in some detail and then examine how they are best put together to form whole functions.

\* \* \*

Academic text books on IC design are often filled with mathematics. It is important to understand the fundamentals, but it is a waste of time to calculate every detail of a design. Let the simulator do this chore, it can do it better and faster than any human being. An analysis will tell you within seconds if you are on the right track and how well your circuit performs. Assuming that you have competent models and a capable simulator, an analysis can teach you more about devices and circuits than words and diagrams on a page.

## 1 Devices

Let's assume your IC design needs an operational amplifier. Which one? If you check the data-books of linear IC suppliers, you'll find hundreds of them. Some have low current consumption, but are slow. Others are quite complex, but feature rail-to-rail inputs and outputs. There are inputs which are factory-trimmed for low offset voltages, outputs for high currents, designs for a single supply voltage, very fast devices, etc.

Here is the inherent problem with analog building blocks: there are no ideal designs, just configurations which can be optimized for a particular application. If you envisioned a library from which you can pull various analog building blocks and insert them into your design, you are about to experience a rude shock: this library would have to be very large, containing just about every operational amplifier (and all other linear functions) listed in the various data-books. If it doesn't, your IC design is bound to be inferior to one done with individual ICs.

In short: *There are no standard analog cells*. If your application is the least bit demanding, you find yourself either modifying previously used blocks or designing new ones. In either case you need to work on the device level, connecting together transistors, resistors and rather small capacitors.

To do this you need to know what devices are available and what their limitations are. But above all you need to *understand* devices in some detail. The easiest way to learn about complex technical things is to follow their discovery, to have the knowledge gained by the earlier men and women (who pioneered the field) unfold in the same way they brought it to light.

#### Semiconductors

In 1874 Ferdinand Braun was a 24-year old teacher in Leipzig, Germany. He published a paper which was nothing short of revolutionary: he had found that some materials violated Ohm's law. Using naturally formed crystals of Galena (lead sulfite, the chief ore mineral of lead) and other sulfites, he pressed a spring-loaded metal tip against their surfaces and observed that the current through this arrangement was dependent on the polarity of the applied voltage. Even more puzzling was the fact that, in the direction which had better conduction, the resistance decreased as the current was increased.

What Braun (who later would give us the CRT) had discovered, we now know as the diode, or rectifier. It was not a very good one, there was only a 30% difference between forward and reverse current. And there were no practical applications. Braun could not explain the effect, nor could anybody else.

In 1879 Edwin Hall of Johns Hopkins University discovered what was later named the Hall Effect: when you pass a magnetic field through a piece of metal it deflects the current running through the metal. In all the metals he tried the deflection was to one side; he was greatly relieved to see that this confirmed the negative charge on the electron.

But then the surprise came. In some materials the deflection went the other way. Where there perhaps positive electrons?

Nothing much happened until about 1904. Radio appeared on the scene and needed a "detector". The signal was amplitude modulated and to make the music or speech audible the radio frequency needed to be rectified (i.e. averaged). Thus, 30 years after Braun's discovery, the "odd behavior" of a wire touching Galena (and now many other materials, such as silicon carbide, tellurium and silicon) found a practical application. The device was called the "Cat's whisker", but it actually didn't work very well; one had to try several spots on the crystal until one was found which produced a loud enough signal.

And it was replaced almost immediately by the vacuum tube, which could not only rectify but amplify as well. Thus the semiconductor rectifier (or diode) went out of fashion.

It was not until 1927 that another practical application appeared: large-area rectifiers. These were messy, bulky contraptions using copperoxide (and later selenium) to produce DC from line voltage, chiefly to charge car batteries. But there was still no understanding of how these devices worked. In the background, mostly at universities and large corporate laboratories, some research went on, despite the fact that there was no semiconductor industry yet. In 1931 A.H. Wilson came up with a complete model of energy bands: electrons exist only at discrete levels, each with a higher energy than the lower one; only two electrons can exist at the same level, but they have opposite spins; at the last (or highest level) are the valence electrons and there is a gap in energy to the ultimate one, the conduction band; once they reached that last level, conduction happens by accelerating the electrons in an electric field.

The theory was fine, but it took 15 years for someone to make a connection between it and the diode.

There were two problems masking the real semiconductor effects. First, all the behaviors so far noticed were surface effects. The cat's whisker applied a metal wire, the copper-oxide and selenium rectifier metal plates. Today this is recognized as a rather specialized configuration, only surviving in the Schottky diode. Second, the semiconductor material was anything but pure, containing elements and molecules which counteracted the desired behavior.

Then World-War II happened and with it came radar. To get adequate resolution, radar needed to operate at high frequencies. Vacuum tubes were too slow, so the discarded "cat's whisker" came into focus again (employed right after the antenna to rectify the wave so it could be mixed with a local oscillator and produce a lower frequency, which could be handled by vacuum tubes).

This time a world-wide emergency drove the effort, with plenty of funding for several teams. They started with the "cat's whisker" and tried to determine what made it so fickle and unreliable. It became immediately obvious that purer material was required, and that this material should be in the form of a single crystal. When they heated part of a crystal close to the melting point and moved the heated zone, the foreign materials moved with it. And now they realized that some of these impurities were actually *required* to get the diode effect. And these impurities all fell into very specific places within the periodic table of elements.

**Silicon** and **germanium** both have a valence of four. Valence simply means that in the outermost layer of electron orbits there are four electrons. Silicon, for example, is element number 14, meaning it has a total of 14 electrons. The first orbit (or energy level) has two electrons, the second eight and the third four.

The outermost orbits of the atoms touch each other and the electrons in this orbit don't stay with one particular atom, they move from orbit to orbit. It is this sharing of electrons that hold the atoms together. And this ability to move from atom to atom is also the basis of electrical conduction: in conductors the electrons roam widely and are easily enticed to move in an electrical field, whereas in an insulator they stay close to home.

Electrically, pure silicon is a terribly uninteresting material. It is an insulator, but not a very good one. The fun begins when we add the right impurities, or dopants.

Just to the right of silicon in the periodic table is **phosphorus**, element number 15. Like Silicon, it has two electrons in the first orbit, eight in the second but there are five in the third. Now let's say we were able to pluck out an atom in a block of silicon and replace it with a phosphorus atom. Four of the valence electrons of this new atom will circulate with the silicon electrons, but the fifth one won't fit in. This excess electron creates a negative charge and the silicon becomes what we now call n-type.

This introduction of excess electrons is unlike static charge. When you brush your hair so that it stands upright, you have simply moved some electrons temporarily. When you "dope" silicon, the charge is permanent, fixed in the crystal lattice (and does not become a battery).

Similarly, to the left of Silicon and one space up in the periodic table is **boron**, element number 5. It has two electrons in a first level and three in a second, a valence of three. If we replace a silicon atom with a boron one, there is an electron missing and we create a positive charge, or p-type material. As with the excess electron in n-type silicon, we can apply an electric field and cause a current to flow, but the net-effect is the flow of holes, not electrons. This is what makes the Hall effect go the wrong way.

It is important to understand this mechanism of moving holes and electrons in doped semiconductors. In n-type material an excess phosphorus electron wanders into the path of a neighboring silicon electron and displaces it. The displaced electron then takes the orbit of another one and so on until the last electron ends up at the starting point, the phosphorus atom.

This endless game of musical chairs - proceeding at near the speed of light - depends greatly on the temperature. At absolute zero there is no movement. At about - $60^{\circ}$ C the movement is sufficient for semiconductor effect to start in silicon. At about 200°C there is so much movement that silicon practically becomes a conductor. It is only within a relatively narrow range, about - $55^{\circ}$ C to 150°C, that silicon is a useful semiconductor.

In p-type material the movement starts with an electron in the neighborhood of the boron atom. It fills the vacancy and then is itself replaced by another electron and so on until the first electron moves away from the boron atom again. The moving is done by electrons, but the net effect is a moving hole.

When an electric field is present the movement takes on a direction: electrons flow toward the positive electrode and are replaced by other electrons flowing out of the negative electrode.

It is amazing how few dopants it takes to make n-type or p-type material. Silicon has  $5 \times 10^{22}$  atoms per cubic centimeter. A doping level can easily be as low as  $5 \times 10^{15}$  boron or phosphorus atoms per cubic centimeter, i.e. one dopant atom for every 10 million silicon atoms. No wonder it took so long to discover the true nature of the semiconductor effects; in nature, the number of miscellaneous impurities is far larger than one in 10 million.

#### The Diode

Even with a dopant present silicon is uninteresting. It is not a good conductor and as a resistor it is inferior to metal film or even carbon. But if we have both n-type and p-type atoms in the same silicon crystal, things suddenly happen.

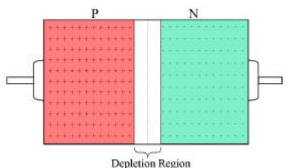

Opposite charges attract each other, so the excess electrons near the border of the n-type section move into the p-type material and stay there. An electron fills a hole and the electric charges cancel each other.

This only happens over a short distance, as far as an electron (or hole) can roam. The resulting region is called the space-charge layer or depletion region.

Now suppose you connect a voltage to the two terminals. If the pregion is connected to the negative terminal of the supply and the n-region to the positive one, you simply push the charges away from each other, enlarging the depletion

If, however, the pregion is positive and the

n-region negative, you push the charges closer together as the voltage increases. The closer proximity forces more and electrons and holes to cross the depletion region. The effect is exponential: at 0.3 Volts (at room temperature) very little current flows; at 0.6 Volts the current is substantial and at 0.9 Volts very large.

The expression for the diode voltage is:

$Vd = \frac{kT}{q} \ln \frac{I1}{Is} \qquad \text{or} \qquad I1 = Is \left(e^{\frac{Vd \cdot q}{kT}} - 1\right)$

where Vd = voltage across the diode

k = Boltzman constant (1.38E-23 Joules/Kelvin)

T = the absolute temperature in Kelvin

q = the electron charge (1.6E-19 Coulombs)

I1 = the actual current through the diode

and Is = diffusion current

Note that 1.38E-23 is a more convenient notation for  $1.38 \times 10^{-23}$ .

The diffusion current Is depends on the doping level of n-type and p-type impurities, the area of the diode and (to a very high degree) on temperature. A reasonable starting point for a small-geometry IC diode is Is=1E-16.

The equations neglect a few things. There is a limit in the voltage that can be applied in the reverse direction. Similar to an arc-over in any insulator, there comes a point when the electric field becomes too large and the opposing charges crash into each other. This *breakdown voltage* depends on the concentration of dopants: the higher the concentration, the lower the breakdown voltage.

There is a price to be paid for high breakdown voltage. As the dopant concentration is lowered, the depletion layer becomes larger and the higher voltage pushes it deeper yet. This distance must be accommodated in the design.

The opposing charges in a semiconductor junction are no different from those on the plates of a capacitor. So every junction has a capacitance; but since the distance between the electrons and holes changes with applied voltage, the capacitance becomes voltage dependent. The lower the voltage, the higher the capacitance, increasing right into the forward direction.

Lastly, there is resistance in the semiconductor material not taken up by the depletion region. For our "typical" concentration of 5E15 (atoms per cubic centimeter, giving a practical breakdown voltage in an IC of about 25 Volts), the resistivity is about 1 Ohm-cm for phosphorus (n-type) and 3 Ohm-cm for boron (p-type). For comparison, aluminum has a resistivity of 2.8 microOhm-cm, copper 1.7 microOhm-cm. Resistivity (p or rho) is measured between opposite surfaces of a cube of material with a side-length (w, h, l) of 1cm (10mm):

$$\mathbf{r} = \frac{R^* w^* h}{l} = \frac{Ohm^* cm^* cm}{cm} = Ohm^* cm$$

(or Ohm-cm)

#### The (Bipolar) Transistor

At the time of the first serious work on the semiconductor diode, Bell Laboratories in New Jersey was already world-famous. It attracted the brightest scientists and, even among those, Bill Shockley was a stand-out. In 1938 Shockley teamed up with Walter Brattain to investigate semiconductors.

The depletion layer intrigued Shockley. There was a faint similarity to the vacuum diode. It occurred to Shockley that, if he could somehow insert a grid into this region, it might be possible to control the amount of current flowing in a copper-oxide rectifier, creating the solid-state equivalent of the vacuum triode. Shockley went to Brattain with the idea and Brattain was amused. The same idea had occurred to him too; he had even calculated the dimensions for such a grid, which turned out to be impractically small. Shockley tried it anyway and couldn't make it work. Brattain had been right.

Shockley was not a man easily defeated, though. He modified his idea and came up with a different principle of operation. He conceived that, since a relatively small number of electrons or holes are responsible for conduction in semiconductors and they each carry a charge, he could place a metal electrode near the surface, connect it to a voltage and thus either pull these carriers toward the surface or push them away from it. Therefore, he thought, the conduction of the region nearest the surface could be altered at will. He tried it -- and it didn't work either. The idea was identical to today's MOS transistor.

The work stopped there; both Shockley and Brattain were assigned to other projects during the war. But in 1945 Shockley was made cosupervisor of a solid-state physics group which included Brattain. Shockley was 35, Brattain 43. The progress made in refining silicon and germanium was not lost on Shockley; he decided to try his idea for an amplifying device again and had a thin film of silicon deposited, topped with an insulated control electrode. It still didn't work; no matter what voltage was applied to the control electrode, there was no discernable change in current through the silicon film. Shockley was puzzled; according to his calculations there should have been a large change. But the effect - if there was any - was at least 1500 times smaller than theoretically predicted.

It was at this time, that John Bardeen, 37, joined Shockley's group. He looked at Shockley's failed experiment and mulled it over in his head for a few months. In March 1946 he came up with an explanation: it was the surface of the silicon which killed the effect. Where the silicon stops, the four valence electrons are no longer neatly tied up by the neighboring atoms. Bardeen correctly perceived that some of them were left dangling and thus produced a surface charge (or voltage), which blocked any voltage applied to an external control electrode.

With this theoretical breakthrough the group now decided to change directions; instead of attempting to make a device, they investigated the fundamentals of semiconductor surfaces. It was a long, painstaking investigation; it took more than a year. On November 17, 1947 Robert B. Gibney, another member of the group and a physical chemist, suggested using an electrolyte to counteract the surface charge. On November 20 he and Brattain wrote a patent disclosure for an amplifying device as tried by Shockley but using electrolyte on the surface. Then they went to the lab and made one. The electrolyte was extracted from an electrolytic capacitor with a hammer and nail. The device worked, the electrolyte did precisely the job that Gibney thought it would.

But, although this "field effect" device amplified, it was very slow, amplifying nothing faster than about 8Hz. Brattain and Bardeen suspected that it was the electrolyte that slowed down the device so, on December 16, 1947, they tried a different approach: a gold spot with a small hole in the center was evaporated onto germanium, on top of the insulating oxide. The idea was to place a sharp point-contact in the center without touching the gold ring, so that the point would make contact with the germanium, while the insulated gold ring would shield the surface. And now, for the first time, they got amplification.

There was only one thing wrong with this device: it didn't work as expected. A positive voltage at the control terminal increased the current through the device when, according to their theory, it should have decreased it. Bardeen and Brattain investigated and found they had inadvertently washed off the oxide before evaporating the gold, so that the gold was in contact with the germanium. What they were observing was an entirely different effect, an injection of carriers by the point contact. They realized that, to make such a device efficient, the distance between the two contacts at the surface needed to be very small. They evaporated a new gold spot, split it in half with a razorblade and placed two point contacts on top. Now the device worked even better and they demonstrated it to the Bell management on December 23, 1947.

For half a year Bell kept the breakthrough a secret. Bardeen and Brattain published a paper on June 25. 1948 and on June 30 a press conference was held in New York. The announcement made little impression; the New York Times devoted a few lines to it on page 46.

Shockley had been disappointed by the turn of events, he had not been part of the final breakthrough. But he realized that, even though there was a working device, the battle wasn't over yet. No-one within the group really understood precisely how the transistor worked. So, in the early days of January 1948 Shockley sat down and tried to figure out what was going on between the two point contacts. And in the process he conceived a much better structure: the junction transistor.

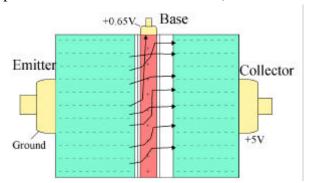

It was a brilliant analysis and holds up to this day. In a bipolar transistor there is a current flowing between the base and emitter terminals, which is a diode. Thus electrons flow from the emitter to the base (so named because in the original point-contact transistor it was the bulk of the material). Since the base is p-doped, these electrons are the *minority carriers* in the base (hence the name bipolar transistor - carriers of both polarities are needed for the effect). A few of them will reach the base

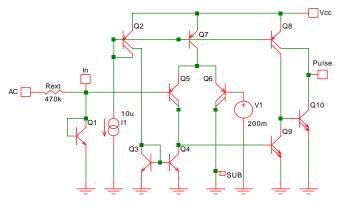

Fig 1-2: The electrons in the base of an NPN transistor are intended to flow to the base terminal but, if the base is very thin, most of them are diverted by the positive potential of the collector.

have a current gain of 100 or even 500.

The bipolar transistor is an odd amplifier, quite non-linear and somewhat difficult to use. Consider the input terminal, the base. It is a diode (with respect to the emitter). You need to lift its voltage up to at least 0.6 Volts (at room temperature) for any current to flow. From that point on the current increases terminal. But if the base is lightly doped and *very thin* most of them will be attracted by the positive collector voltage before they re-combine with a hole in the base. In a good transistor 100 or even 500 of the electrons will be side-tracked to the collector while one goes to the base terminal. Thus we

Fig. 1-3: The current flow and gain of an NPN transistor.

exponentially, both in the base and the collector. It is not a linear voltage amplifier; only the currents have a (more or less) linear relationship.

Also notice that the emitter current is always larger than that of the collector, since it contains both the collector and base current.

We have shown here an NPN transistor. If we reverse all the doping and the voltages we create a PNP transistor. It works the same way in every respect except that it is a bit handicapped: it is slower and has a lower gain; holes, now the minority carriers in the base, just don't move as well as electrons.

The point-contact transistor was a nightmare to manufacture and had very poor reliability. Also, these devices were made from germanium, which has a rather limited useful temperature range. The junction transistors were made by alloying dopant materials on either side of a flat piece of germanium or silicon. It was difficult to make the base uniformly thin and the process created considerable leakage current.

The next big step was again invented at Bell Labs: diffusion. At room temperature gases mix even if they are held perfectly still. This happens because each atom or molecule moves around randomly due to the energy it receives by temperature. The higher the temperature, the more pronounced is this movement and thus the mixing or diffusion. If the temperature is high enough (e.g. over 1000°C) such gases can even diffuse into solid material, though their diffusion speed decreases enormously. Thus, for example, silicon exposed in a high-temperature furnace to n-type impurity (gas) atoms develops an n-layer at its surface with a depth as far as the impurities penetrate. This may require a temperature close to the melting point of silicon and take several hours for a penetration of just a few micro-meters, but it is far more controlled than alloying.

Moreover, you can dope repeatedly. Suppose you have a piece of silicon which has been doped n-type. If you diffuse p-type impurities into the surface, you convert a layer from n-type to p-type if there are more ptype impurities than n-type. The junction is located at the depth at which the two impurities are equal in concentration. A second diffusion of a yet higher concentration can then convert the material back to n-type again. However, you have to pay attention to the fact that subsequent exposure to high temperature causes any previous layer to diffuse further.

There are a few more dopants available too: p-type gallium (rarely used) and n-type arsenic and antimony. The latter two have the advantage that they diffuse more slowly than phosphorus or boron. For this reason they are primarily used early in the process and are thus less affected by subsequent diffusions.

When, in 1956, the three inventors of the transistor were awarded

the Nobel Prize for physics, only Walter Brattain was still at Bell Laboratories. John Bardeen had left in 1951 to become a professor at the University of Illinois and, for his research there in superconductivity, he received a second Nobel Prize in 1972.

Bill Shockley left Bell Labs in 1954. Banking on his reputation, which had risen proportionally to the acceptance of the transistor, he managed to strike a deal with the Beckman Instruments Company. A subsidiary, called the Shockley Semiconductor Laboratories, was set up in Palo Alto, California. Shockley's fame had risen to such a height that he could pick some of the best people. Within a year he had some 20 people - predominantly Ph.D.s - working for him, among them Robert Noyce, 28, Gordon Moore, 27, and Jean Hoerni, 32.

For all of these people there was a brief period of fascination after they joined. But then the true Bill Shockley appeared from behind the glitter of fame and they discovered that Shockley was, in fact, a rather erratic and unpleasant man. He would fire his employees for minor mistakes, throw tantrums over trivial problems and change directions for no apparent reasons. He incessantly tried innovative management techniques, such as posting everybody's salaries on the bulletin board.

Noyce and Moore were pushing Shockley to make silicon transistors using the diffusion approach. Shockley wasn't interested; his hope was for his laboratory to come up with an entirely new device, a device which would represent as large a step over the transistor as the transistor had been over the vacuum tube.

Now totally dissatisfied, the crew talked to Arnold Beckman, the president of the parent company, and informed him of the impossible situation. Beckman promised to hire a business-minded individual who could act as buffer between Shockley and his staff. But the solution didn't work, Shockley refused to let go of the day-to-day decision-making. Out of patience, eight staff members reached a deal with the Fairchild Camera and Instrument Company and, in October 1957, the group departed.

The new company, called Fairchild Semiconductor, was at first an independent operation, with Fairchild Camera and Instrument holding an option for a buy-out. The product they began to develop was the one they had proposed to Shockley. The detailed structure of this device, called the Mesa transistor, had been tried in germanium before, but not in silicon. It required two diffusions, both into the same side of a silicon wafer. The first diffusion was p-type, the second n-type, and the difference in depth between the two layers created the base region which, for the first time, could be made with a high degree of accuracy. The top surface of the transistor was then masked with wax and the exposed silicon etched away, giving the

remaining piece a mesa-like shape.

Because of its superior performance, sales of the Mesa transistor took off almost immediately, reaching \$ 7 million in 1959. But there were also problems. The most serious one concerned the reliability of the Mesa transistor. The etched silicon chip was soldered onto the bottom of a small metal case, leads were attached to the top regions and then the case was welded shut. Tiny metal particles, ejected during the welding process, floated around inside the case and kept on shorting out the exposed p-n junctions.

Silicon rapidly grows a thin oxide layer when it is exposed to air. This is better known as glass (silicon-dioxide) and its growth can be enhanced by moisture at high temperature. Some of the dopant gases used in diffusion (such as gallium) can penetrate this oxide layer, while others are stopped by it. There was, therefore, a possibility that the oxide layer could be used as a mask. If the oxide were to be etched off in some places but not in others and suitable dopant gases used, diffusion would take place only in the areas without oxide. But a study done at Bell Laboratories came to the conclusion that an oxide layer exposed to a diffusion is left contaminated and must subsequently be replaced by a freshly grown one.

This bothered Hoerni. He didn't see any reason why the oxide layer could not be used as a diffusion mask for both diffusions -- provided he would use dopant gases which were stopped by the oxide - and why the oxide should subsequently be regarded as contaminated. So he tried it -- as an unofficial side project -- and out of the trial came an advance ranking in importance second only to the transistor itself: the *planar* process.

In preparation for the first diffusion Hoerni spread a photosensitive and etch-resistant coating (photoresist) over the top of the oxide and exposed it through a photographic plate (mask) carrying the patterns of the base regions, using the photographic techniques already developed for "printed" circuits. The subsequent etching then only removed the oxide in the regions where p-type impurities were to be diffused. After the diffusion he closed these oxide "windows" again by placing the wafer in hightemperature moisture and then repeated the steps for the second (emitter) diffusion. In a third masking step windows could then be etched in the oxide to make contact to the two diffused layers. He then evaporated aluminum onto the top surface of the wafer and patterned it with the same photographic techniques. The wafer could then be scribed (like glass) and broken into individual transistor chips.

The planar process had a whole series of advantages. Of most immediate importance was the fact that the junction was automatically protected by the oxide, one of the best insulators known. No longer could the metal particles from the welding of the case short it out. Secondly, photographic methods could be used to delineate not just one but hundreds of transistors simultaneously. Thus individual, delicate masking of each transistor was no longer required, giving the planar transistor a huge potential for reduced cost. Noyce, who was by now the general manager, saw the advantage of the planar process and quietly moved it into production.

There was another advantage to the planar transistor: once the dopant enters the silicon it diffuses in all directions, including sideways. The P-N junction, therefore, ends up underneath the oxide, never exposed to either human handling or the contamination of air. For this reason the planar junction is the cleanest (and most stable) junction ever produced. Fairchild's customers who, in early 1959, didn't know that their transistors were now being manufactured by an entirely new process, were surprised to find leakage currents one thousand times smaller than those of previous shipments.

While Fairchild flourished, Shockley Transistor went downhill. It was sold twice, then closed in 1969. Shockley became interested in sociology and announced a theory called "dysgenics", which proposed that poor people were doomed to have low IQs. By the time he died in 1989 his reputation was ruined.

#### **The Integrated Circuit**

In July 1958 Jack Kilby of Texas Instruments conceived that a block of germanium or silicon could be host to not only transistors and diodes, but resistors and (junction) capacitors as well. This appeared to be enough of a variety to make a small circuit, all of it in the same block of silicon.

The idea was good, but his approach cumbersome. To insulate the various components from each other Kilby etched the silicon, in some areas all the way through. To connect them together he used gold wires. The circuit was very small to be sure, but it was a production nightmare. Each tiny block of silicon had to be made individually, including the patterning, etching and wiring. When TI's attorneys prepared a patent application they looked in horror at the Rube Goldberg-like drawings and had Kilby put in some words saying that interconnection could also be made by laying down a layer of gold. How this could be done over this three-dimensional landscape he didn't say.

While Kilby was working on his circuits in Texas, a similar but far more elegant idea occurred to Robert Noyce in California. Noyce's

motivation was primarily cost, not size. He realized that it didn't make sense to fabricate precisely arranged transistors on a wafer, cut them apart, place them in a housing and arrange them again in on a circuit board; if the additional components on the circuit board could be placed on the wafer, a considerable number of manufacturing steps could be saved. Noyce had no problem visualizing capacitors and resistors made in silicon, he was constantly dealing with these (unwanted) effects. What was needed, though, was an inexpensive way to connect all these components on the wafer. The idea of using wires had no chance in Noyce's mind, it would have simply been too expensive. But he saw that, in the planar process, this problem was already solved: the aluminum layer used to connect the transistors and the wires could also be used between the components.

In1959 Noyce entered his idea into his notebook and filed for a patent application. Kilby's and Noyce's patent applications were clearly in interference and a bitter battle between the two companies started in the courts. Texas Instruments won because Kilby application mentioned a thin film of gold, thus seemingly anticipating Noyce. Fairchild appealed.

While the two patents were fought over in the courts, neither TI nor Fairchild could collect any royalties for integrated circuit, which were already showing explosive growth. So the two companies came to an agreement, declaring Kilby and Noyce co-inventors of the integrated circuit. Shortly after this the appeals court handed down its decision: Noyce, not Kilby, was declared the inventor of the IC.

It could not have been otherwise. Even today every single IC is made exactly as Noyce described it, while Kilby's approach has long been abandoned. But the most important contributor to the invention of the IC was clearly Jean Hoerni with his planar process, for which he has never been adequately recognized. The planar process rates as one of the great inventions of the 20th century.

Robert Noyce died in 1990 at age 62. In 2000 Jack Kilby won the Nobel Prize for the invention of the integrated circuit

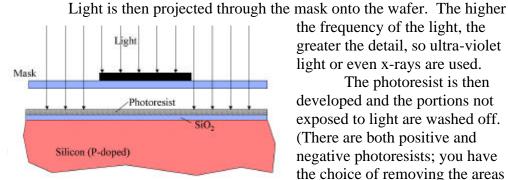

Let's take a closer look at a basic processing step in the Planar process. First, you need a mask, a piece of flat glass, with an opaque pattern on it. The pattern has been generated optically or, more likely, with an electron beam.

The silicon wafer is first oxidized, i.e. a thin  $SiO_2$  layer is grown, for example by exposing the wafer to steam in a furnace. Instead of oxide, nitride or a combination of oxide and nitride is also used. On top of the oxide a thin layer of "photoresist" is spread, a light-sensitive emulsion similar to that on a photograph.

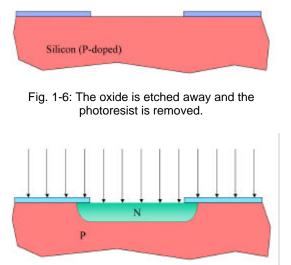

Fig. 1-4: The first step: A light-sensitive and etch-resistant layer (photoresist) is spread on the wafer and exposed to light through the mask.

Fig. 1-5: The photoresist is developed like a photograph and the wafer is ready for etching.

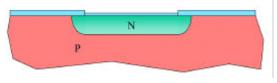

Fig. 1-7: A gas containing N-type dopants (boron, arsenic or antimony) diffuses slowly into the surface of the wafer at high temperature.

the frequency of the light, the greater the detail, so ultra-violet light or even x-rays are used.

The photoresist is then developed and the portions not exposed to light are washed off. (There are both positive and negative photoresists; you have the choice of removing the areas which are either exposed or not exposed to light).

Next the entire wafer is immersed in an acid which removes the oxide in the areas where it is not protected by the photoresist. In more modern processes a plasma is used; acid etches not only downward but also slightly sideways underneath the photoresist, while plasma etches downward only.

The wafer is then placed into a furnace (a quartz tube heated to greater than 1000°C). A gas carrying the desired dopant (in this case boron, arsenic or antimony) swirls around the wafer and slowly diffuses into the surface.

Note two important facts here: 1. There is a crowding of dopants near the surface of the silicon. With time they will diffuse deeper into the silicon, but there will always be more dopants near the surface. Thus any diffused region has a marked gradient. 2. Dopants not only diffuse downward, but also sideways. (Since supply is more

limited at the very edge, the side-ways diffusion extends to only about half the distance of the downward one). This places the junction (where n = p) underneath the oxide and is thus never exposed to the (dirty) environment.

After diffusion the exposed silicon surface is covered again by an oxide layer so that the wafer is ready for the next masking step, which could

Fig. 1-8: After the diffusion the oxide is regrown, ready for the next masking step.

be another diffusion or the etching of contact holes.

There is an important feature here, which should not go unnoticed.  $SiO_2$  is glass, which is transparent to light. The light is reflected at the bottom of the oxide by the

silicon and interference patterns are created, i.e. the sum of direct and the reflected light eliminates some frequencies. Thus the color of the oxide layer depends on its thickness. This not only makes for beautiful photographs but, more importantly, it allows subsequent masks to be precisely aligned with previous ones.

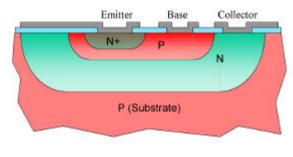

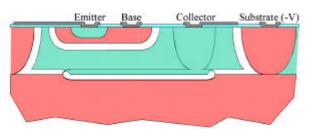

Here then is one form of an NPN transistor made with the planar process. The substrate (the starting wafer) is doped p-type as the silicon is grown. There are three diffusions in succession, the first being rather deep. After the diffusions, contact holes are made (with the same basic photoresist process), aluminum is deposited over the entire wafer, patterned (another photoresist step) and etched away where it is not wanted.

Fig. 1-9: A simple planar NPN transistor.

Alas, this transistor has a rather significant shortcoming: high collector resistance. The current has to flow through the region between the base and the substrate. That is the far end of the collector diffusion, the end which has the fewest dopant atoms and therefore the highest resistance.

Since the invention of the planar process a few more ways of fabricating have been added:

**Epitaxy**. If you strip a silicon wafer of its oxide and put it into a furnace which is filled with gas containing not only a dopant but also silicon, you can grow a doped single-crystal layer. As the atoms carried by the gas deposit themselves on the surface of the wafer, they will align

themselves according to the existing crystal structure.

You can also precede this by diffusing regions into the original wafer, so that you will have areas of high concentration underneath the **epitaxial layer**. Even though these regions are buried, it is still possible to align subsequent diffusions to them. When a diffused area is re-oxidized, a small amount of silicon is consumed (the Si in SiO<sub>2</sub>), thus creating a small depression in the surface. The edges of these depressions are visible at the top surface of the epitaxial layer, though the image tends to be blurry and is shifted (in most processes) along the crystal axis (around  $45^{\circ}$ ).

**Ion Implantation**. You can literally shoot dopant atoms into silicon by electrically charging (ionizing) them and then accelerating them with a high voltage (several hundred thousand volts). The treatment is somewhat brutal, the newly arrived atoms don't end up neatly aligned in the crystal structure and an annealing heat cycle is necessary to let the atoms align themselves into a crystal structure.

The number of dopant atoms introduced is generally more accurate in ion implantation than in diffusion. Also you can aim implantation for a certain depth (but not very deep). In the subsequent heat cycle (and during subsequent diffusions) the dopant atoms will diffuse and thus widen the layer. The maximum concentration, however, is then not at the surface, but at a chosen depth.

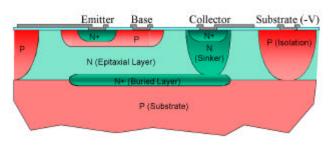

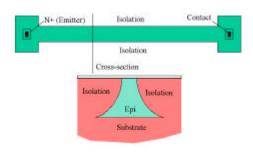

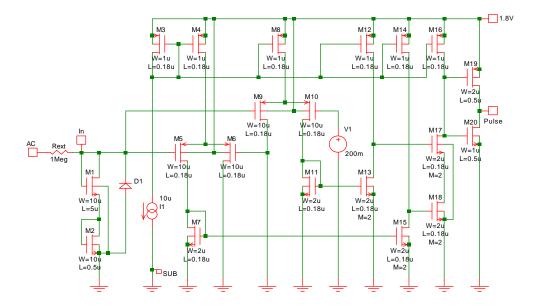

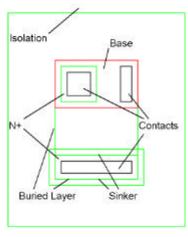

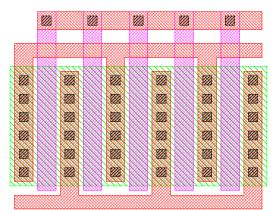

We now have arrived at a modern NPN transistor as made in a bipolar (or BICMOS) process. Before growing the epitaxial layer, a heavily doped (thus N+) **buried layer** is diffused (or ion implanted) into the p-type substrate. During epitaxy it diffuses somewhat, both into the substrate and the new epitaxial layer.

Fig. 1-10: A much improved planar, integrated NPN transistor. The buried layer and sinker lowers the collector resistance.

The next diffusion is the **isolation**. It is deep (and, therefore, also wide); it has to connect up with the substrate, so that the entire n-type collector region is surrounded by p-type regions. A second ntype diffusion connects up with the buried layer

(and the emitter N+ diffusion is used on top of it simply because it's available at no cost). Now the collector current has a (fairly) low-resistance path.

This transistor is isolated from its neighbors (and other components) as long as the substrate is held at the most negative voltage in the circuit (**junction isolation**). In this way the collector-substrate junction is always reverse-biased and only leakage current (pico-amperes) flows.

There are some flaws and limitations in the performance of this or any other bipolar transistor:

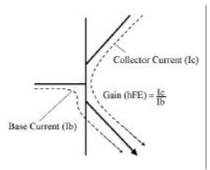

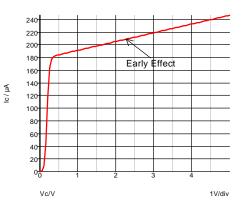

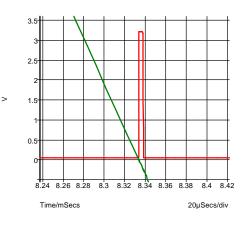

**Early Effect**, named after Jim Early (then at Bell Labs, later at Fairchild), who explained it first. Ideally the collector current should be equal to the base current multiplied by a constant gain (hFE or beta). But, as we have seen above, each p-n junction has two depletion layers. For the collector-base junction, one depletion layer extends into the collector, the other into the base. The base is almost always more heavily doped than the

collector, so its depletion layer is fairly shallow. However, the base is also very thin, so even a shallow depletion layer takes up a significant portion of the base depth. As the collector voltage increases, the depletion layers widen. In the collector region this has little effect (as long as it doesn't hit the other side of the collector), but in the base region it narrows the base-width. Since the gain of a bipolar transistor is very much dependent on the base-width, the gain simply increases as the effective base-width decreases.

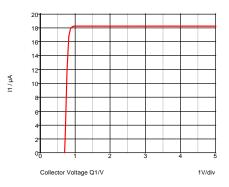

Fig. 1-11: Even with a constant base current the collector current increases with the collector-emitter voltage because the depletion layer narrows the base-width.

If you draw a straight line, extending the slope (from 0.4 to 5 Volts) into the negative quadrant and let it intersect with the zero-current line, you get the **Early Voltage**. In this case, for a 5-Volt process, the Early voltage is -15 Volts (but is generally expressed as 15V). Depending on the chosen base-width, it can be less than that and the slope correspondingly steeper.

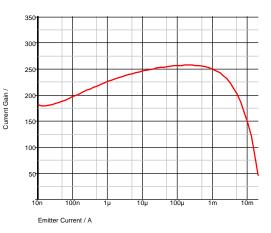

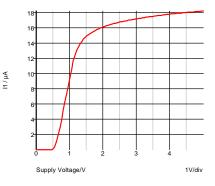

**Gain versus Current**. For any bipolar transistor the current gain falls off both at low and high current.

First, the low end. There is always a leakage current across any junction; for a perfectly clean surface this is the diffusion current. In the base-emitter junction this leakage current takes away a portion of the supplied base current. In our graph here the current shunted by leakage at the low end (10nA Ie, or about 50pA Ib) amounts to 33% of Ib, i.e. the gain has dropped by one third.

If you extend this plot to much lower current, you will see the gain rise to almost infinity. This is nothing more than the effect of the collectorbase leakage current.

At the high end two effects take place simultaneously: 1. The number of electrons present in the base simply becomes so large that they are no longer the minority carriers and the whole effect comes to a halt. 2.

The base current must flow from the contact to the flat area between the emitter and collector. At low current this is no problem, the resistance in the base is sufficiently small. But as the collector current increases (and with it the base current), the resistance in this flat region of the base causes a significant voltage drop, and the far end gets less current. Eventually, as the current is increased even more, only the edge of the emitter on the side of the base contact is active. Thus

Fig. 1-12: The current gain (hFE) of a bipolar transistor drops off both at low and high currents.

the high-current capability of a bipolar transistor is determined not by the

emitter area, but by the active emitter length, i.e. emitter periphery to which the base can supply current through low resistance. A good starting point for the maximum current (at which the gain drops to 50%) is 1.5mA per um of active emitter length, but this value varies from process to process.

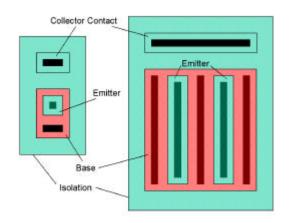

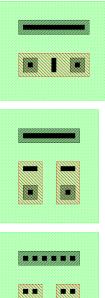

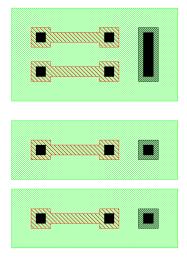

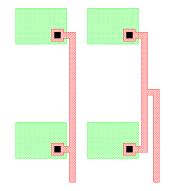

To increase the current capability of a bipolar transistor you can place base contacts on both sides of the emitter and lengthen the emitter. Shown here on the left is the top view of a minimum-geometry transistor and on the right a version for higher current.

To make the life of a designer easier, the isolation pattern is usually drawn as a rectangle and then inverted when making the mask, i.e. the isolation diffusion is actually *between* devices, not in the device area.

Many processes require that all contacts be the same size, in which case the contact rectangles must be broken up into small, identical (and properly spaced) squares.

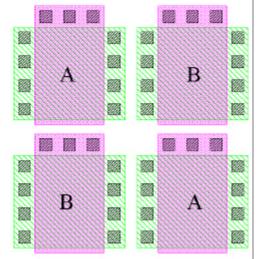

Be aware, that transistors of different sizes (as drawn here) do not match well. At low current a large emitter area produces a higher gain than a small one, because the minority carriers have a higher chance to be captured by the collector. If you want to produce a precise ratio, use only one emitter size and identical base contacts. The emitters can be in a common base area and the collector size is of no consequence except for collector resistance (or saturation voltage).

**Substrate Current**. There is only leakage current across the collector-substrate junction, unless the transistor saturates.

Assume the collector is connected through a resistor to the positive supply voltage and the base is driven so hard that the collector voltage drops to near the potential of the emitter (termed saturation).

There are now two diodes in parallel and the base current has two paths; the new one forms a PNP transistor with the NPN base becoming the emitter, the NPN collector the base and the substrate the collector. Since the NPN collector is much larger than its emitter, some (or all) of the base current flows to the substrate.

There is little danger in this, except when you drive the base very hard, trying to get the lowest possible collector voltage, or if you have many saturating NPN transistors. The path in the substrate from a transistor to the -V connection has some resistance. If the substrate current is so large

Fig. 1-14: When an NPN transistor saturates a stray PNP device leaks current to the substrate.

that the voltage drop across this resistance can forward-bias some substratecollector junction on the way, you may get some really bad effects, including latch-up.

**Maximum Voltage**. To get a high operating voltage requires high resistivity - low doping concentration. But there is a price to be paid: the depletion regions become wide.

Let's use the integrated NPN transistor as an example. There are two depletion regions, one extending into the epitaxial layer from the base (downward and side-ways), the other into the epitaxial layer from the isolation. To make sure the first one does not reach the substrate (and thus

Fig. 1-15: At higher operating voltage the depletion regions around the NPN transistor become larger.

cause premature breakdown or **punchthrough**), the epitaxial layer must be deep which means that the isolation diffusion must be deep, and thus wide. Look at the left side of the transistor.

The spacing between the

isolation (as drawn) and the base must accommodate the following:

the side-ways diffusion of the isolation, the isolation-collector depletion region, a safety margin for possible misalignment, the collector-base depletion region and the side-ways diffusion of the base.

In addition there is also a high-voltage depletion layer each between the base and the sinker and the sinker and the isolation, as well as a deeper (and thus wider) sinker. All this adds up to a painfully large area.

The increase in area can be curbed somewhat by two measures: 1. Use an additional diffusion for the isolation by creating a P+ region directly underneath the normal one before growing the epitaxial. The two halves will then diffuse toward each other (**up-down diffusion**) and meet in the middle, thus requiring only half the depth and width; 2. Add more processing steps, creating both low-voltage and high-voltage devices on the same wafer.

**The Miller Capacitance**. As we have seen above, the bipolar transistor is a very non-linear (exponential) voltage amplifier and cannot thus normally be used as one. But it *has* a voltage gain, and a high one at that (several hundred is not uncommon).

There is an unavoidable junction capacitance between the collector and the base. If you feed a current with an ac signal into the base, the voltage change on the collector will be much larger than that on the base. Thus, looking into the base, the junction capacitance appears *multiplied* by the voltage gain (the Miller effect). Instead of a tiny fraction of a pico-Farad you have to deal with 10 or even 100pF. If the base is fed from a high impedance (e.g. a current source), the frequency response is then nowhere near the advertised  $f_t$  (cutoff frequency).

This Miller effect can be reduced by circuit design techniques (e.g. a **Cascode Stage**), but even so most circuits cannot operate much above say 1/20 of  $f_t$ . ( $f_t$  is the frequency at which the current gain drops to 1).

On the other hand, there is also a benefit. In feedback amplifiers you almost always need a **compensation capacitor** (more of this later). Using the Miller effect you can get away with a 5pF capacitor, which appears to be as large as 1nF, a value which would be much too large to be integrated.

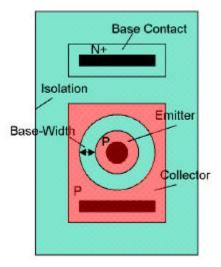

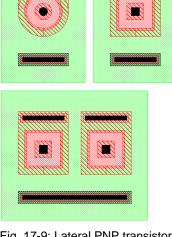

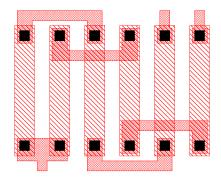

#### The Case of the Lateral PNP Transistor

It is the world's worst transistor, you couldn't sell it as a discrete component: low cutoff frequency, very limited current range and an inferior noise figure. But no self-respecting analog IC designer would want to be without it. The reason: In either a CMOS or bipolar process no additional diffusions are required.

The emitter and collector are formed by the base diffusion (in a bipolar process) or the p-channel source/drain diffusion (in a CMOS process). The current thus flows radially (or laterally) along the surface from the emitter to the collector.

The doping levels are all wrong. For optimum performance you would want the emitter to have a very high concentration, the base somewhat lower and the collector quite low (to accommodate the higher collector voltage). Here the emitter and collector doping levels are equal, and the base is much higher. Thus, to allow space for the depletion regions,

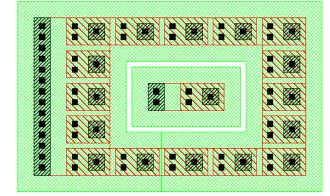

Fig. 1-16: The lateral PNP transistor.

the base width (the distance between the collector and emitter, minus the side-ways diffusions) needs to be quite large. Hence the slow speed (it takes time for the carriers to travel across the base). Figure on an  $f_t$  in the neighborhood of 30MHz with an operating voltage of 15 Volts; at lower voltages the base-width can be narrower which increases  $f_t$  but also makes the Early effect more pronounced.

Despite of all of this, with good surface control you can get a gain in excess of 100. But the current range is limited, rarely exceeding 100uA for a minimum geometry device.

And there is somewhat of a problem with substrate current. There is a competing PNP transistor, using the same emitter and base, but with the substrate (and the isolation diffusion) as the collector. In normal operation a current about half the magnitude of the base current flows from the emitter to the substrate terminal. When the lateral PNP transistor saturates, the substrate current becomes almost equal to the collector current. If you

don't have a buried layer, it gets quite a bit worse.

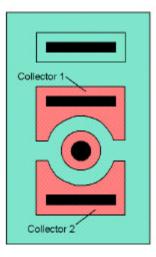

One advantage of the lateral PNP transistor: the collector can be split into two (or more) sections. The emitter current, flowing radially outward is collected by the segments according to their length at the inside. There is a small loss in gain because of the gaps, but the matching between the two collector currents is excellent.

In a CMOS process emitter and collector are usually formed by the p-type diffusion of a p-channel MOS transistor. The intervening space (the base-width) is the same as a p-channel gate, with poly-silicon on top. Connect the poly region to the PNP emitter; it will act as a static shield and have a (slight) beneficial effect.

Fig. 1-17: A split-collector lateral PNP transistor.

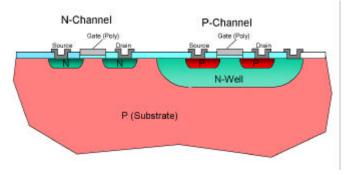

#### **CMOS Transistors**

It took almost 20 years after the invention of the bipolar transistor for MOS to make its appearance. Shockley (and many others) had thought of this device first, it was (or should have been) much more simple: put a plate close to the surface of silicon, connect it to a voltage and move the carriers inside the silicon electro-statically.

The problem was the surface of silicon. Here the silicon atoms are no longer neatly tied up with each other by sharing the outermost electrons. They face an entirely different material, SiO2 (or worse, some covering with unknown impurities mixed in). This material doesn't even have a crystal structure, it is amorphous. In 1964 a startup, General Microelectronics, felt it had licked the problem with CMOS and brought out the first digital MOS integrated circuit. It was one of the worst products ever to hit the market: a large portion stopped working within days. The reason: there were elements with the silicon-dioxide (chiefly sodium) that carried an electric charge and could move. One day the MOS transistor was perfectly functional, the next day it was permanently turned on.

It took another few years to gain an understanding of MOS surface physics and make stable MOS transistors. Today the silicon surface is so well understood that we can deliberately place a charge into the oxide layer that stays there for years, probably even centuries. It is now the dominant integrated device, being much smaller than the bipolar transistor. (The number of MOS transistors produced every year has long surpassed the number of ants in the world. At the time of writing this book, semiconductor manufacturers produced some 500 million transistors for every person in the world per year).

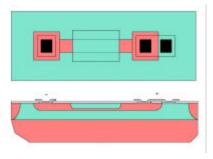

Fig. 1-18: Cross-section of an N-well CMOS process.

The figure shows a cross-section of the most often used (n-well) process. There are many variations and refinements; this is only the basic one. In the gate area the insulating layer (SiO2 or nitride, or a combination) is

thinned down and silicon is grown on top of it. Since the insulator is amorphous, the grown silicon is not single-crystal, it consists of many small crystals which do not fit together very well (thus it is called poly-crystalline silicon or simply **poly**).

Next the source and drain regions are implanted, using a mask. The inside edges are masked by the gate, so they align perfectly to the gate (i.e. they are **self-aligning**). The device is also **self-insulating**: as long as the source and drain are at or above the substrate potential (usually ground), the junctions to the substrate are reverse-biased and no bulky isolation diffusion is necessary.

For the p-channel transistor the polarities for the source and drain implants are reversed and these regions are placed inside an n-type diffusion. In most applications one such n-well hosts many p-channel transistors and is simply connected to the positive supply voltage; in this way the devices are insulated from each other as long as each source and drain is at or below the positive supply.

In both the n-channel and p-channel transistors, sources and drains are identical, i.e. you can arbitrarily call one the source and the other the drain. Or one region can do double-duty, being the drain for one transistor and the source for the next one, connected in series.

The p-channel transistor is always at a disadvantage, because holes are more difficult to move than electrons. Thus it will have a lower gain than an n-channel device (for the same gate oxide thickness) and be

somewhat slower. (MOS transistors, by the way, are called **unipolar** devices, because they employ only one type of carrier, as opposed by the bipolar transistor, in which both electrons and holes are important for the operation).

Now let's look at an (n-channel) MOS transistor in more detail. The basic idea is to create a region (a channel) between source and drain which has the same polarity (n-type), so that

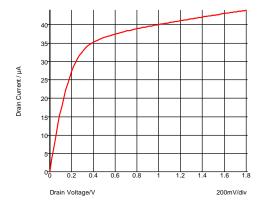

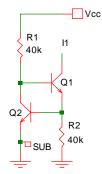

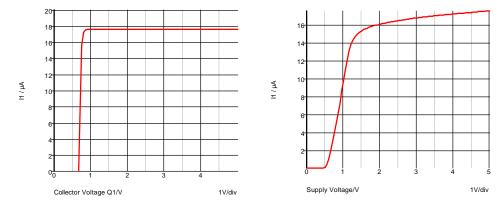

Fig. 1-20: Drain current vs. drain voltage with the gate voltage held constant.

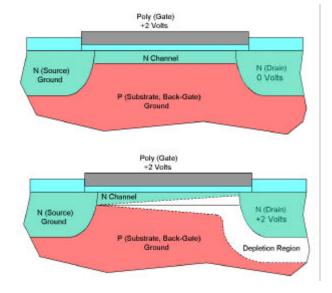

Fig. 1-19: As the drain voltage is increased, a depletion region pinches off the channel.

there is direct conduction between the two. This is done with a positive voltage at the gate which pushes holes away from the surface and the device is called an **enhancementmode** transistor (there are also **depletion-mode** devices in which a channel is implanted or diffused and then cut off with a negative gate voltage).

This is true only at zero or very low drain voltage. As the drain voltage is increased, a depletion region forms around it. Since there is now a voltage drop along the channel, with the drain side at a higher voltage than the source, the depletion region along the channel gradually increases toward the drain, cutting more and more into the channel. Thus the resistance of the channel increases.

The initial slope of the drain voltage / drain current curve is the resistance of the channel without any depletion layers. The final slope at the highest drain voltage represents its resistance with the depletion layer almost pinching off the channel. It is an unfortunate fact that this region is called the "saturation region", which clashes badly with the earlier definition for the bipolar transistor.

Above a certain gate potential, which has to be exceeded

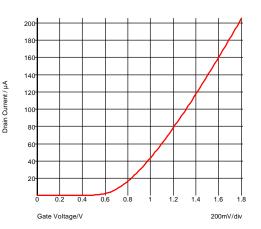

Fig. 1-21: Drain current vs. gate voltage with the drain voltage held constant.

to attract any carriers to the surface (the **threshold voltage**) an MOS transistor is basically a square-law device: doubling the gate voltage results in four times the drain current. The measure of gain is the **transconductance**, drain current divided by gate voltage. So again, like the bipolar transistor, this is a non-linear device:

$$Id = k \frac{W}{L} (Vgs - V_T)^2$$

where Id = drain current k = transconductance W = channel width L = channel length Vgs = gate-to-source voltage  $V_T = threshold voltage$ or  $Vgs - V_T = gate voltage above the threshold$

The region below the channel also influences the gain. It forms a **back-gate**. In an n-well n-channel transistor this is the substrate, common to all devices. You have no choice but to connect it to the lowest negative

voltage. But there is a choice for the p-channel transistor. If you place all the p-channel transistors in a common n-well, you get the smallest total area and therefore the lowest cost. But if the source of such a transistor is operated *below* the positive supply, the back-gate (the n-well) pinches off the channel further and you get a reduced gain (by perhaps 30%). You can avoid this by placing this transistor in its own n-well.

#### The Substrate PNP Transistor

In either a bipolar or CMOS process there exist layers which can form a PNP transistor with the substrate as the collector. Since the collector is permanently connected to the most negative supply voltage, such a device has limited use. In a bipolar process a lateral PNP transistor has greater flexibility and better performance and is thus almost always preferred.

In a CMOS process the same is true, but because of historical reasons or limited information the substrate transistor is still present. The p-type implant for the p-channel transistor forms the emitter, the n-well the base and the substrate the collector. The n-well has a large depth, thus the PNP base-width is large and the gain rather small (e.g. 10).

#### Diodes

There are several p-n junctions in an integrated circuit, each and every one a diode. But few of them can actually be used by themselves without unpleasant side-effects.

Take a simple bipolar process. There are three types of junctions:

Fig. 1-22: Properly connected diodes in a bipolar process.

emitter/base, base/collector and collector/substrate (all referring to the NPN transistor). The last one is hardly ever useful because the substrate is permanently connected to the most negative supply voltage. The base/collector diode is, as we have seen, part of a substrate PNP transistor with a gain; a current perhaps ten times the magnitude of the diode current will flow to the substrate.

The emitter/base junction makes a good diode, but it has a low breakdown voltage (about 6 Volts) and the base has a fairly high resistance. You could connect the surrounding collector to the most negative supply voltage and thus keep it always reverse-biased. But a much better diode results if you short collector and base together, creating a **diode-connected transistor**. The transistor is active, it has gain. Only a small fraction of the current flows through the base, which divides the base resistance by the current gain. This connection in fact gives you an almost ideal diode over about five decades of current.

If the emitter/base breakdown voltage is too low, consider a diodeconnected lateral PNP transistor. This devices has the full operating voltage of the process, but it is limited in current (see above).

In a CMOS process the restrictions are even more severe. The only free-floating junction is between the p-channel source/drain and the n-well. But, as we have seen, these are also part of the substrate PNP transistor. Were you to run a current through this junction, a current of about ten times its magnitude would flow to the substrate.

The term "diode-connected" is often used for an MOS transistor with its gate and drain connected together. Don't be misled by this term: there is no diode as in "junction" diode.

#### Zener Diodes

In a bipolar process the base-emitter diode almost always has a low breakdown voltage (perhaps 6 Volts) with a fairly low temperature coefficient, which makes it useful as a reference voltage.

But exercise care with this device: the same junction is also used as a fusible device.

At low current (e.g. less than 100uA for a minimum-geometry device) the Zener diode behaves well. As you increase the current the region between the emitter contact and the edge of the emitter diffusion lights up faintly (a plasma, which you can observe under a microscope, with all lights turned off). At some high current level a thin aluminum strip is formed abruptly underneath the oxide, which converts the Zener diode into a short-circuit. This effect is used for trimming and carries the earthy name Zener-zapping.

Such a Zener diode is also somewhat noisy. For lower noise (and better accuracy) use a bandgap reference.

Moving an n-channel and p-channel source/drain diffusion in a CMOS process close together so that they intersect can also result in a useful low breakdown voltage, but data for such a device are rarely available from the wafer-fab.

There are also **buried Zener diodes**, devices with a special diffusion below the surface of the wafer. Such devices have lower noise, but the addition to the process tends to be costly.

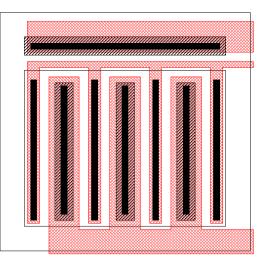

#### Resistors

Every free-floating layer in an integrated circuit can, when properly patterned, become a resistor. But for all of them this is only a secondary duty; their intended application is in a transistor, which is the hardest device to make. It shouldn't come as a surprise then that their values have a higher variation and greater temperature coefficient and their range is more restricted than that of even the least expensive discrete resistor.

Discrete resistors can be tested and adjusted during manufacturing. In ICs the manufacturing is done while the silicon is red-hot, at which temperature it is no longer a semiconductor; you have to wait until it cools down to measure any parameter.

What saves the integrated resistor is its natural ability to match well. Whatever error may have occurred in making one applies to any other on the same wafer. They may both be as much as 25% high in value, but both will be high by (almost) exactly the same amount.

The resistance of any material is given by

$$R = \frac{rho \cdot l}{A}$$

where rho  $(\rho)$  = resistivity in Ohm-cm

l = length

A = area (cross-section)

If we make a square, i.e. w = l, then we get a measure of resistance which is independent of size, the **sheet resistance**, in Ohms per square (or Ohms/ $\Box$ ).

Note the term is sheet resistance, not sheet resistivity. A square in a layer with a sheet resistance of 100 Ohms per square always measures 100 Ohms from one side to the other no matter how large the square.

In a bipolar process the layer most often used for resistors is the (NPN) base (about 200 Ohms/ $\Box$ ). The emitter layer is more heavily doped and thus has a lower sheet resistance (as low as 5 Ohms/ $\Box$ ).

In a CMOS process you have a wider choice: the n+ and p+ diffusions (implants) for the drains and sources, the n-well and usually two different poly layers. Of these the p+ diffusion (about 150 Ohms/ $\Box$ ) and one of the poly layers (around 50 Ohms/ $\Box$ ) are generally best suited.

Sheet resistances depend greatly on the process; you should use the

values given here only as a starting point and get the actual data (including temperature coefficients and tolerances) from the wafer fab.

Diffused resistors must be placed in an island of opposite doping and this island must be connected to a bias voltage so that the junction is reverse-biased. For example, a (p-type) base resistor must be in an n-type (epi) island. This island (sometimes called the "tub") can contain just one resistor or all of them, but its voltage must be at a level equal to or greater than the largest voltage on any resistor. In this case the easiest and safest connection is to +V.

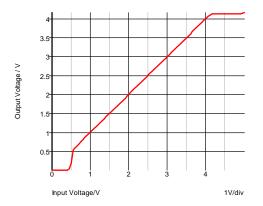

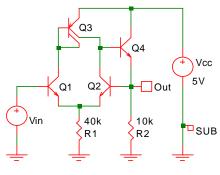

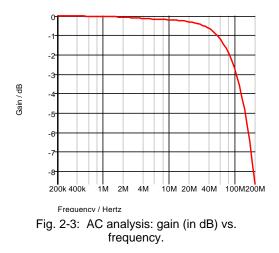

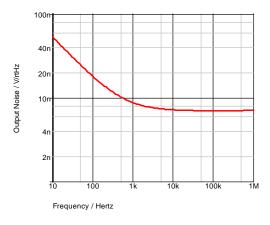

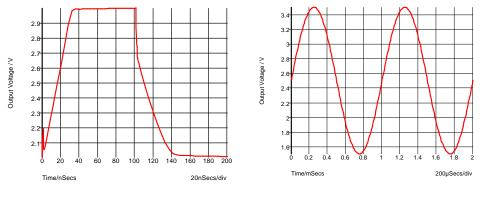

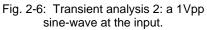

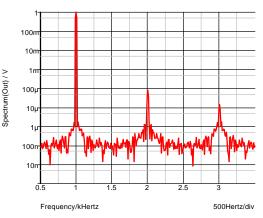

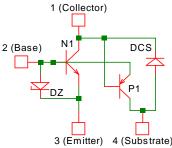

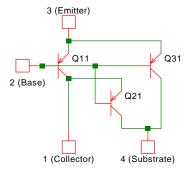

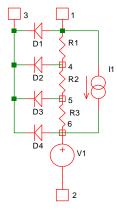

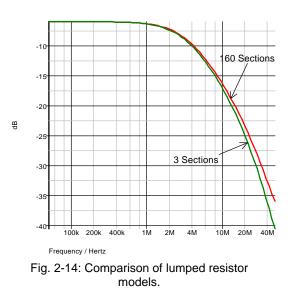

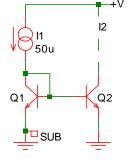

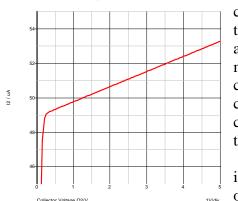

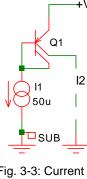

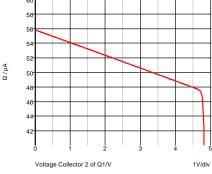

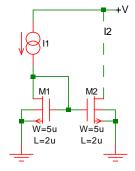

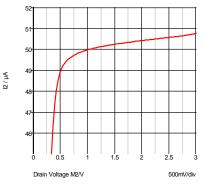

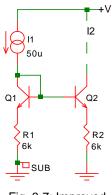

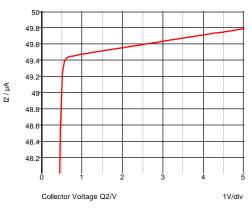

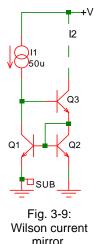

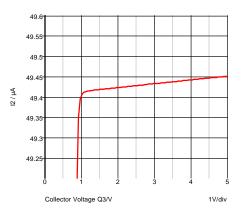

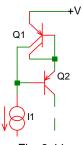

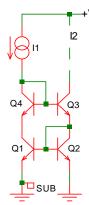

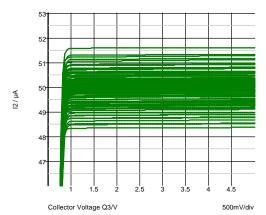

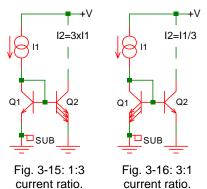

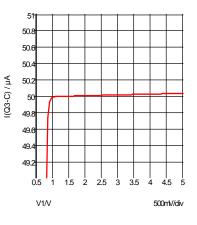

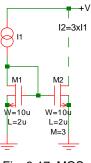

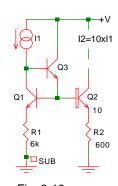

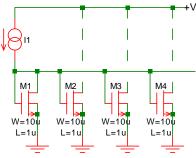

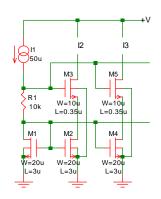

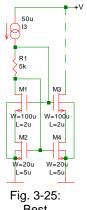

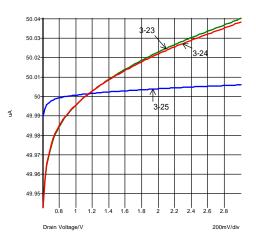

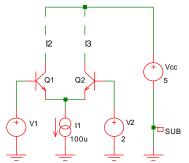

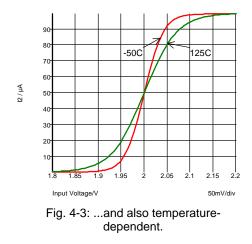

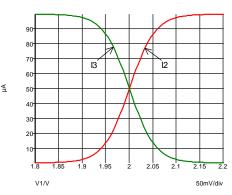

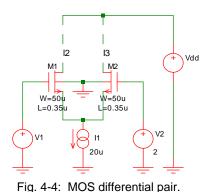

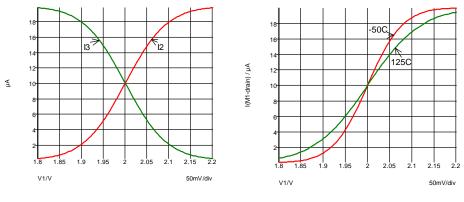

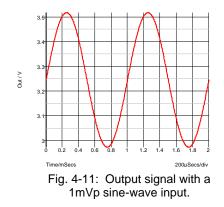

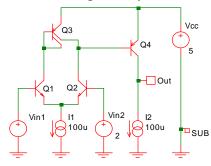

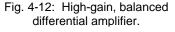

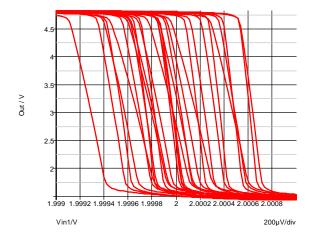

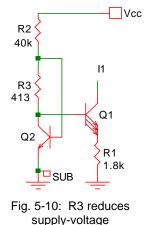

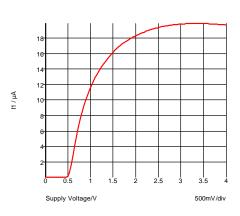

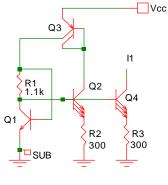

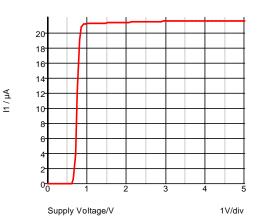

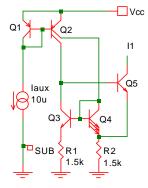

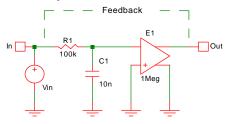

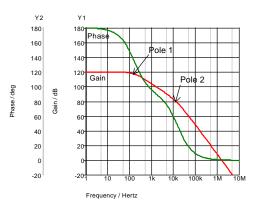

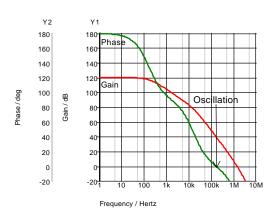

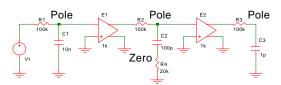

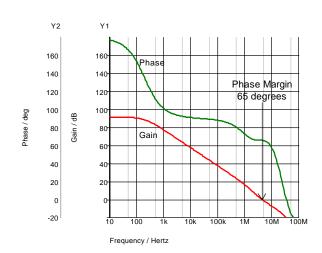

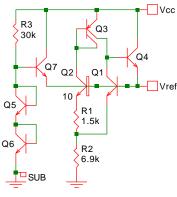

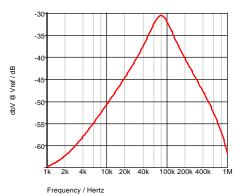

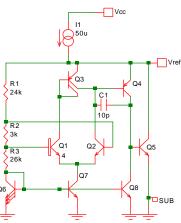

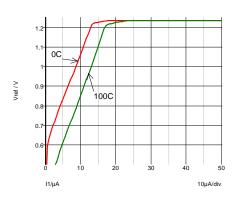

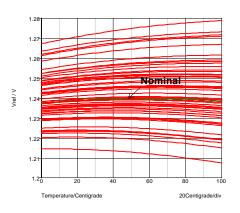

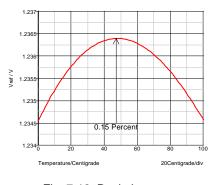

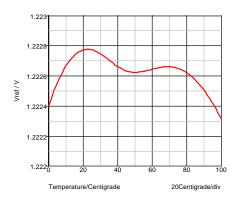

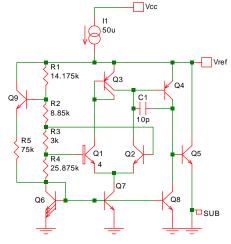

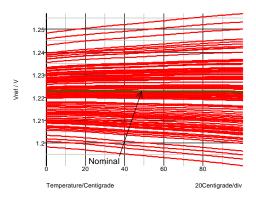

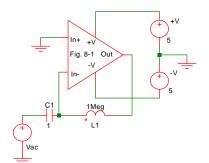

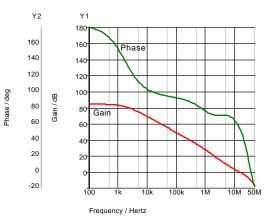

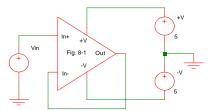

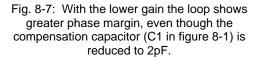

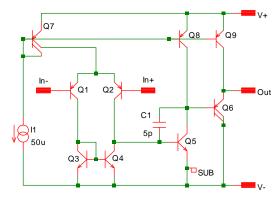

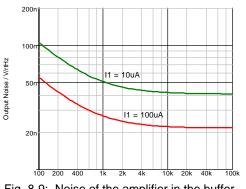

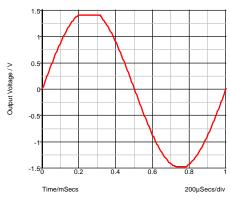

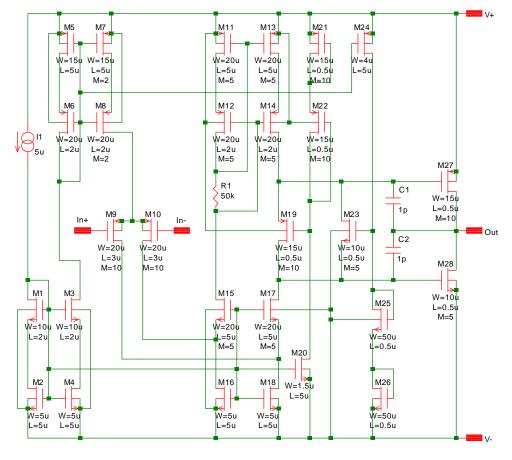

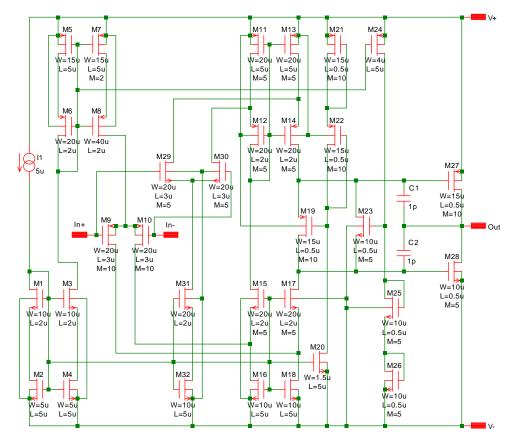

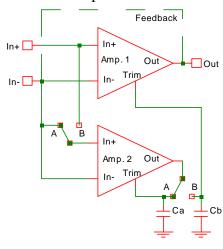

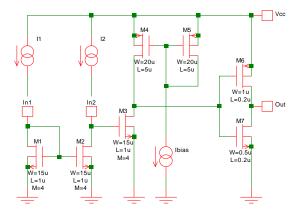

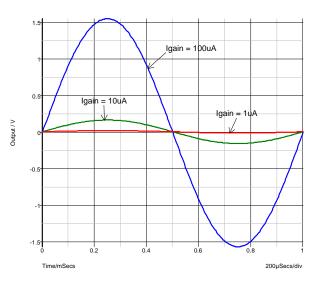

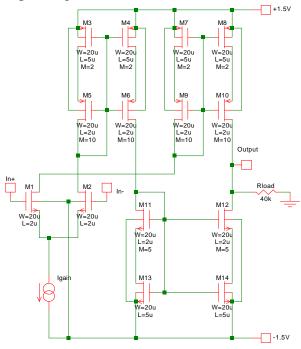

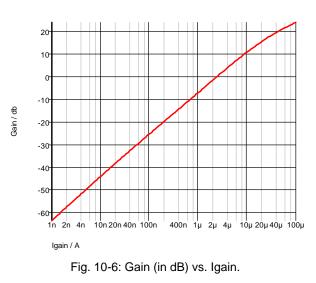

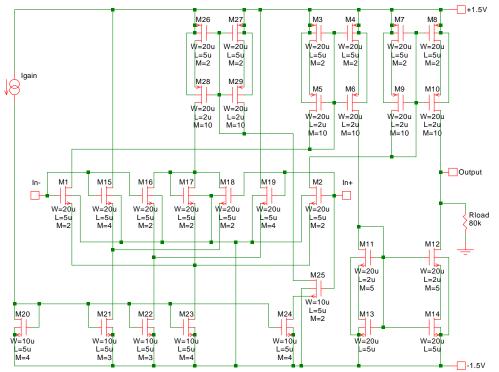

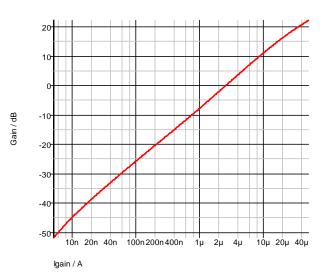

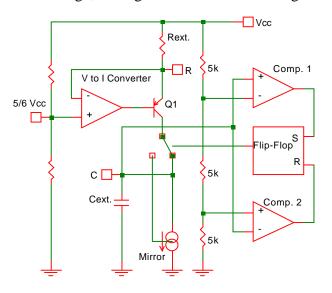

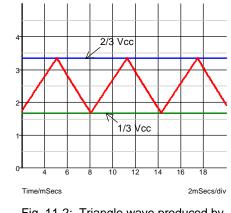

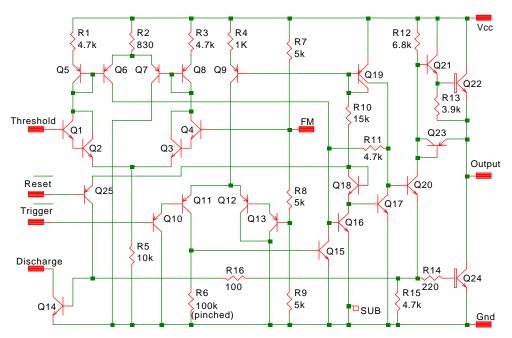

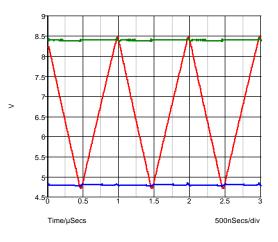

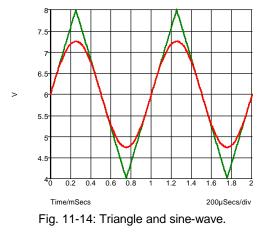

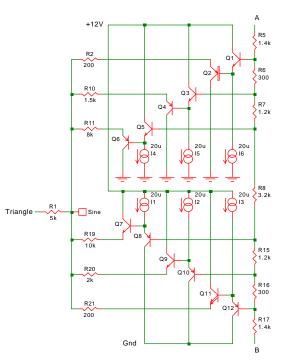

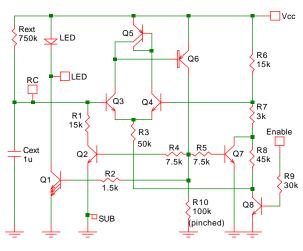

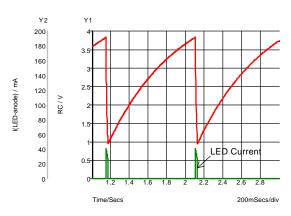

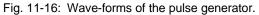

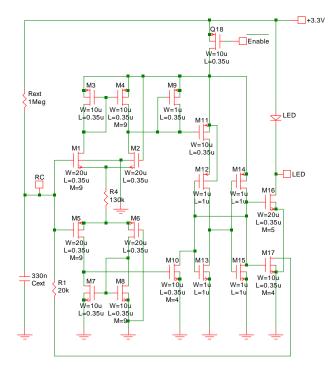

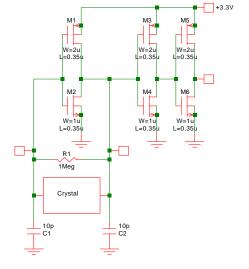

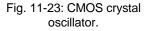

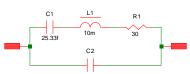

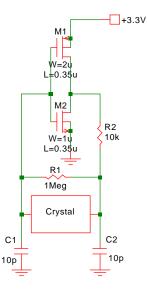

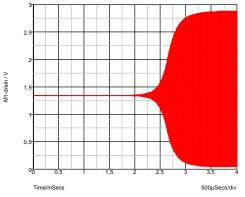

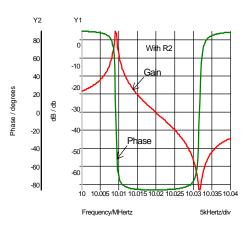

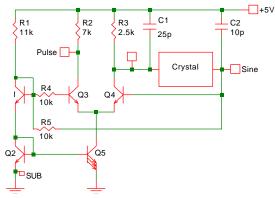

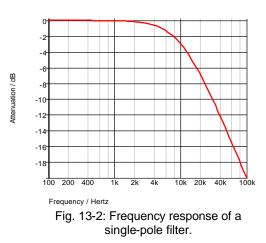

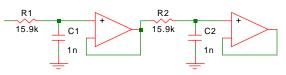

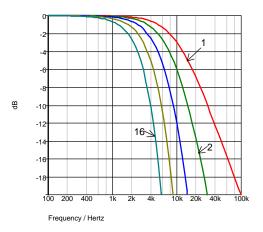

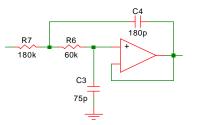

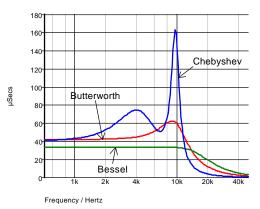

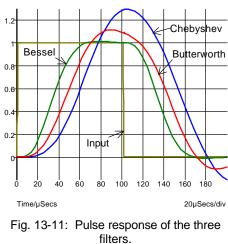

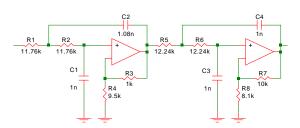

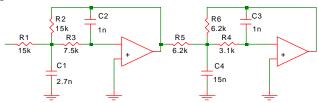

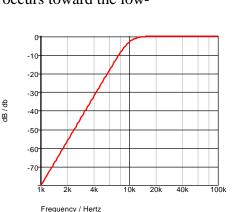

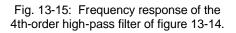

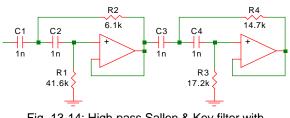

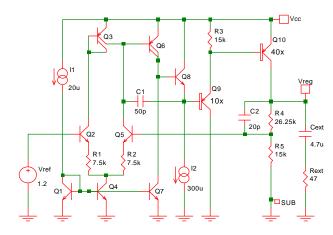

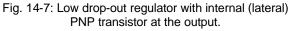

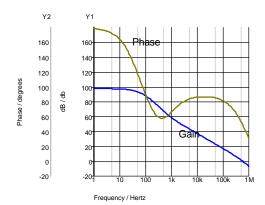

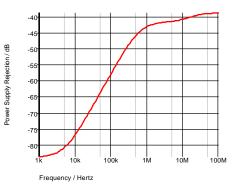

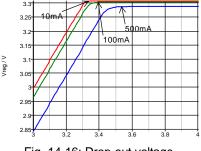

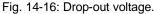

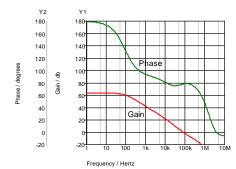

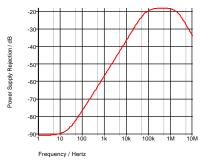

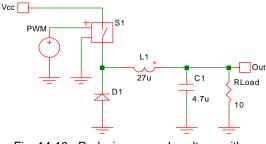

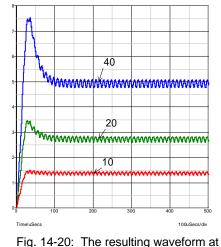

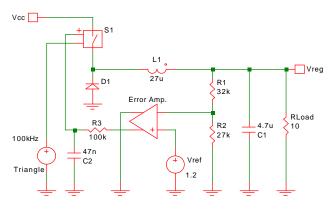

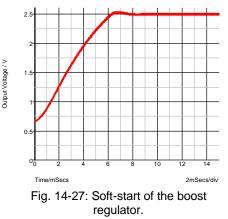

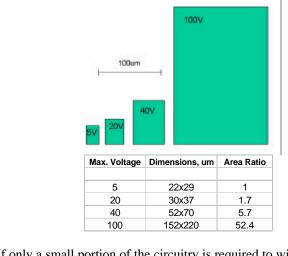

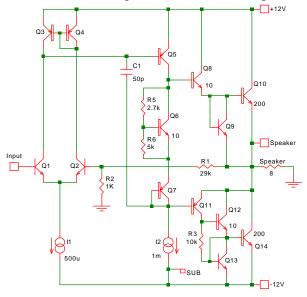

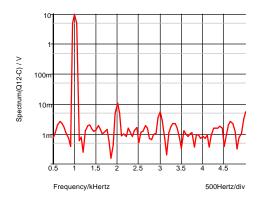

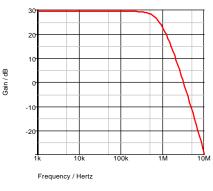

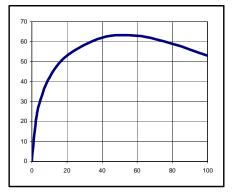

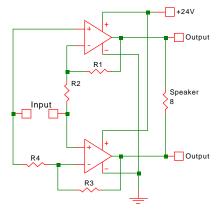

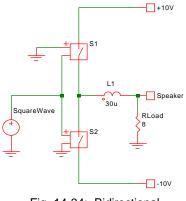

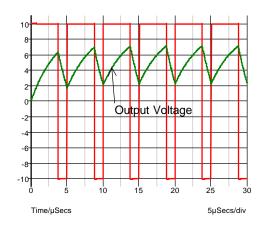

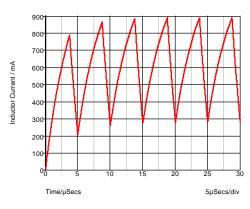

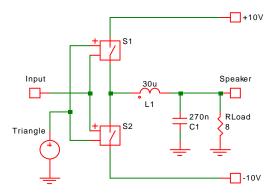

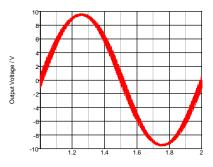

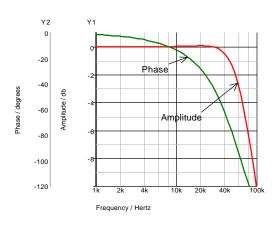

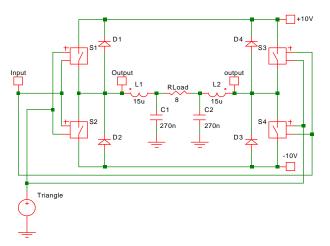

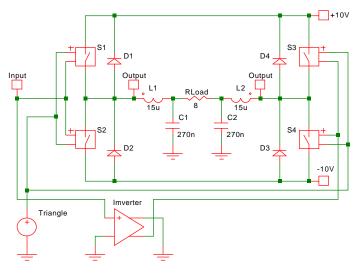

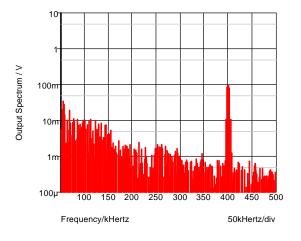

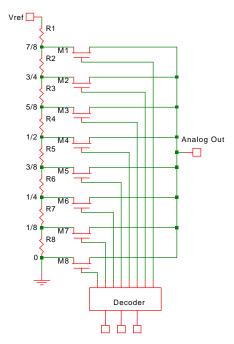

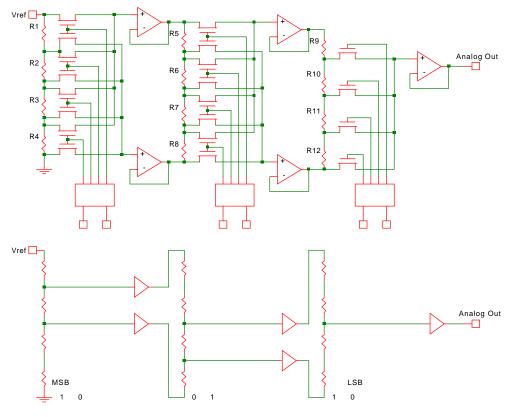

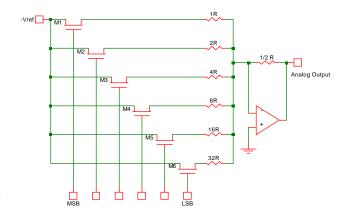

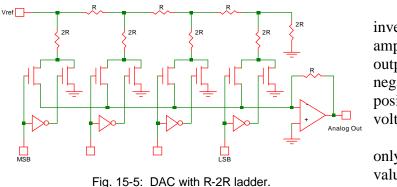

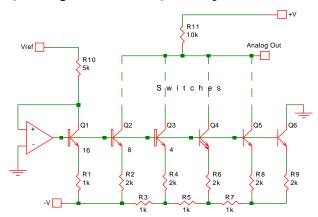

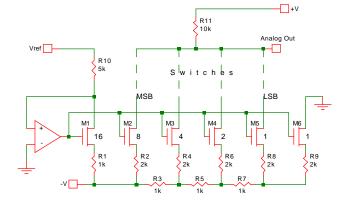

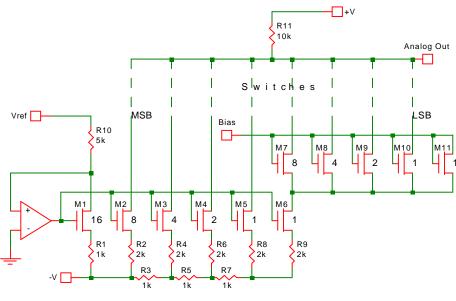

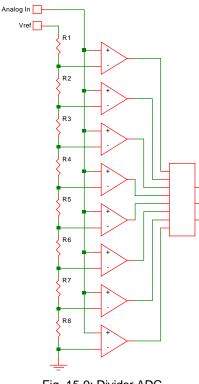

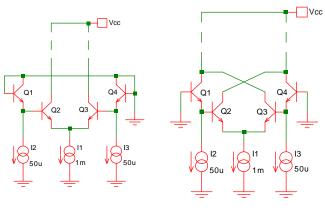

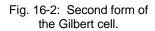

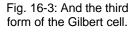

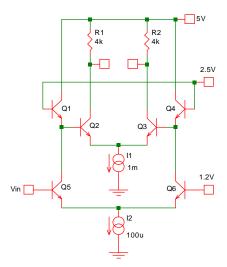

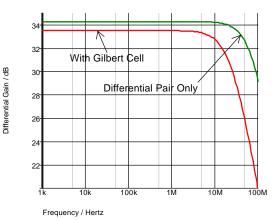

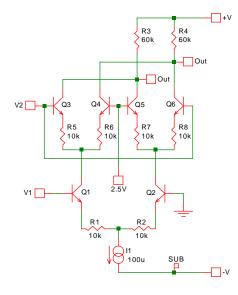

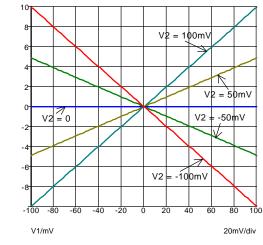

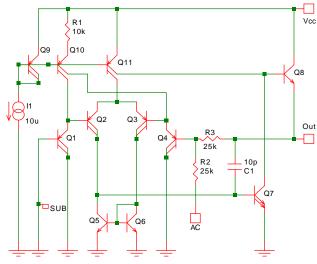

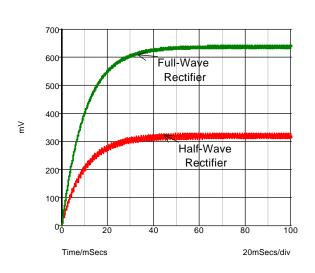

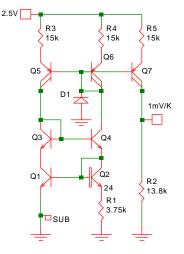

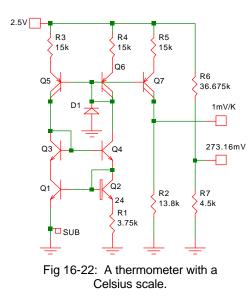

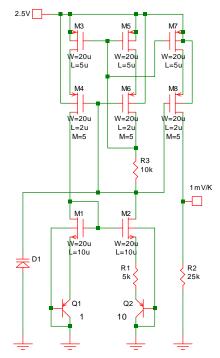

Diffused resistors (and to a lesser degree, poly resistors) have a **voltage coefficient**. The biased surrounding layer pushes a depletion region into the resistor, reducing its cross-section. As the difference in voltage between the resistor and the surrounding layer becomes larger, the depletion region widens, the cross-section becomes smaller and the resistance increases. This effect is especially pronounced in lightly doped layers: the n-well in CMOS and **implanted resistors** in a bipolar process. (The latter uses an additional implant to create a high sheet resistance).